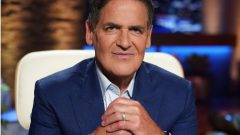

Taiwanský gigant TSMC je na prahu ďalšieho veľkého míľnika v oblasti polovodičového priemyslu. Na nedávnom North American Technology Symposium spoločnosť oznámila plány na rozšírenie svojej technológie balenia čipov CoWoS (Chip-on-Wafer-on-Substrate), ktorá umožní výrobu multičipletových procesorov výrazne väčších, než sú tie súčasné.

Aktuálne riešenia CoWoS podporujú interpozéry s plochou až 2831 mm², čo je viac než trojnásobok veľkosti bežnej fotomasky obmedzenej technológiou EUV litografie. Táto technológia je už využívaná v produktoch ako AMD Instinct MI300X či Nvidia B200, ktoré kombinujú veľké výpočtové čipsety so zásobníkmi pamätí HBM s vysokou priepustnosťou. O téma informoval portál Techspot.

S narastajúcimi požiadavkami na výkon v oblasti AI a HPC aplikácií sa však dopyt po ešte väčších množstvách kremíka naďalej zvyšuje. TSMC preto pripravuje novú generáciu CoWoS-L, ktorá by mala byť dostupná už v budúcom roku. Táto technológia umožní výrobu interpozérov až do veľkosti 4719 mm² s rozmermi substrátu 100×100 mm, čo podporí až 12 zásobníkov HBM.

Trojnásobné zvýšenie výkonu a nové rozmery

Podľa projekcií TSMC by čipy vyrobené touto technológiou mohli priniesť viac ako trojnásobný nárast výpočtového výkonu v porovnaní s dnešnými najvýkonnejšími návrhmi. Cieľom je napríklad pripraviť pôdu pre budúce generácie GPU od Nvidie, ako je plánovaná séria Rubin.

Ešte ambicióznejšie plány zahŕňajú vývoj ešte väčšieho balenia s interpozérom veľkým 7885 mm², namontovaným na substráte s rozmermi 120×150 mm, čo je veľkosť porovnateľná s bežnou CD obálkou. Tento krok by mohol hostiť štyri 3D-stohované systémy na čipe, 12 HBM4 pamäťových zásobníkov a viacero IO čipov.

Pre extrémne náročné aplikácie ponúka TSMC aj technológiu System-on-Wafer (SoW-X), ktorá umožňuje integráciu celých waferov do jedného čipu. Aj keď túto technológiu zatiaľ využívajú len špecializované firmy ako Cerebras či Tesla, očakáva sa širšie uplatnenie v budúcnosti.

Výzvy v napájaní a chladení obrovských čipov

S rastúcou veľkosťou čipov však prichádzajú aj technické výzvy. Dodávanie energie do týchto veľkých zostáv si vyžaduje inovácie, keďže takéto čipy môžu spotrebovať kilowatty energie. TSMC preto integruje pokročilé napájacie obvody priamo do substrátov CoWoS-L, využívajúc technológiu N16 FinFET.

Zníženie elektrického odporu, zlepšenie integrity napájania a stabilizácia napätí pomocou hlbokých kapacít umožňujú dynamickú zmenu napätí a rýchlu reakciu na meniace sa pracovné zaťaženia.

Rovnako dôležitým problémom je tepelné riadenie. Nové čipy generujú obrovské množstvá tepla, čo núti výrobcov hľadať riešenia ako priamy kvapalinový chladiaci systém či ponorné chladenie. TSMC už spolupracuje s partnermi na vývoji systémov na chladenie dátových centier ponornými technológiami, avšak ich integrácia priamo do balenia čipov ostáva výzvou.

Ďakujeme, že čítaš Fontech. V prípade, že máš postreh alebo si našiel v článku chybu, napíš nám na redakcia@fontech.sk.

Teraz čítajú

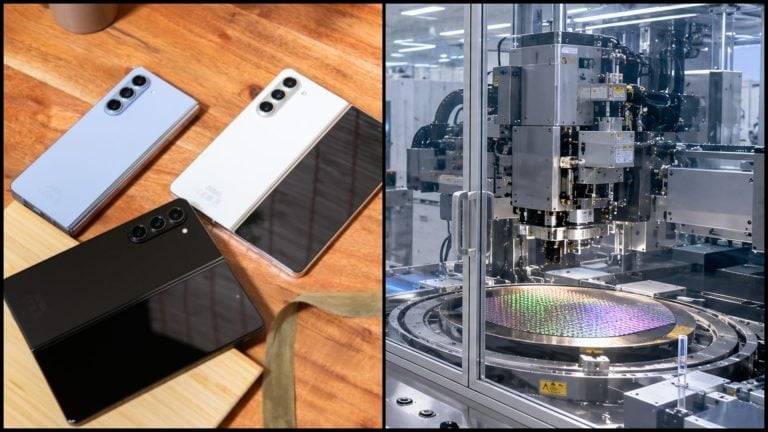

Samsungu hrozí najväčší štrajk v histórii. Zamestnanci sa vyjadrili, ceny elektroniky sa môžu zvýšiť

7 minút mu tlieskali v stoji. Nové sci-fi ohúrilo divákov, šokuje brutálnou akciou

Pri Jeruzaleme našli záhadný 50-metrový tunel, ktorý šokoval vedcov. Jeho účel je stále nejasný

Nolan reaguje na posmešky aj zhrozených historikov. Odysea vznikala rovnako ako Interstellar

Kým Európa rieši clá, Čína chystá brutálnu ofenzívu. Automobilky môžu ťahať za kratší koniec

NAJČÍTANEJŠIE ZO STARTITUP

Detoxikačné kúry nepotrebuješ: Odborníčka vyzdvihuje lacnú zeleninu, ktorá chráni pečeň a redukuje hmotnosť

PREMIUM

PREMIUM„Väčšine klientov už hypotéka nevyjde,“ varujú experti. Banky pritvrdili posudzovanie

„Je to ako robiť s opitým stážistom.“ Mark Cuban varuje pred novodobým fenoménom, ktorý ľuďom ničí kritické myslenie

Vodičáky čaká najväčšia zmena za desaťročia: Brusel pripravuje nové pravidlá pre milióny šoférov

AKTUÁLNE: Kauza langošov má dohru. Pokutu zrušili, šéf finančnej správy sa išiel ospravedlniť osobne

- 24 hod

- 48 hod

- 7 dní

-

- Poklad z doby bronzovej prišiel z iného sveta, analýza materiálu odhalila zvláštny pôvod

- Stačila jedna noc. Slováci na Netflixe podľahli historickému veľkofilmu

- Je rozhodnuté. Najväčší akčný hit súčasnosti spoznal svoju budúcnosť

- BYD došla trpezlivosť: Bloger musí zaplatiť státisíce eur za ohováranie

- Do Ameriky doletí za 90 minút. Prelomové lietadlo v prvých testoch všetkých prekvapilo

-

- Stačila jedna noc. Slováci na Netflixe podľahli historickému veľkofilmu

- Poklad z doby bronzovej prišiel z iného sveta, analýza materiálu odhalila zvláštny pôvod

- Slováci kupujú zbytočne obrovské televízory. Pozerajú na horší obraz a bolia ich oči

- Na ČSFD má 86 %. Jeden z najlepších filmov roka ukáže ako sa vysnívaný sen môže zmeniť na nočnú moru

- Očakávané sci‑fi 2026 malo byť novým začiatkom. Kritici sú však rozdelení

-

- Stačila jedna noc. Slováci na Netflixe podľahli historickému veľkofilmu

- Poklad z doby bronzovej prišiel z iného sveta, analýza materiálu odhalila zvláštny pôvod

- Program na večer je jasný. Na Netflix práve dorazil nový veľkofilm Ridleyho Scotta

- Juiced Nomadix je elektrická motorka, ktorá prepisuje pravidlá. Ponúka výkon 15 kW a vynikajúcu cenu

- Slováci kupujú zbytočne obrovské televízory. Pozerajú na horší obraz a bolia ich oči

Rusi opäť provokujú NATO. Úrady v európskom meste zatvorili školy

Dôležitý krok: Kia štartuje výrobu modernizovaného modelu na Slovensku

Európsky štát stavia obrovské batériové úložisko. Pomôže pri návale zelenej energie

Nový zdroj plynu pre Európu je spustený. Poľsko už odoberá surovinu zo severu

Zlá správa pre Slovensko. Minuli sme svoje prírodné zdroje na celý rok

Európa rieši riziko nedostatku paliva. Ohrozené môžu byť spoje na dovolenky

EÚ poriadne pritvrdila. Zakáže najnemorálnejšie aplikácie na trhu

NAJČÍTANEJŠIE ZO STARTITUP

Detoxikačné kúry nepotrebuješ: Odborníčka vyzdvihuje lacnú zeleninu, ktorá chráni pečeň a redukuje hmotnosť

PREMIUM

PREMIUM„Väčšine klientov už hypotéka nevyjde,“ varujú experti. Banky pritvrdili posudzovanie

„Je to ako robiť s opitým stážistom.“ Mark Cuban varuje pred novodobým fenoménom, ktorý ľuďom ničí kritické myslenie

Vodičáky čaká najväčšia zmena za desaťročia: Brusel pripravuje nové pravidlá pre milióny šoférov